题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

设计一个可以控制计数功能的计数器,当X=0时,计数器以二进制数序列000、 001、010、011、 100、101、110、111计数并重复。当X=1时,计数器以格雷码序列000、001、 011、 010、 110、111、101、100计数并重复,要求:(1)画出计数器的状态图和ASM图;(2)用Verilog HDL语言描述系统的工作过程。

答案

答案

查看答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“设计一个可以控制计数功能的计数器,当X=0时,计数器以二进制数序列000、 001、010、011、 100、101、110、111计数并重复。当X=1时,计数器以格雷码序列000、001、 011、…”相关的问题

更多“设计一个可以控制计数功能的计数器,当X=0时,计数器以二进制数序列000、 001、010、011、 100、101、110、111计数并重复。当X=1时,计数器以格雷码序列000、001、 011、…”相关的问题

第2题

第4题

第5题

第7题

A.ENP=1;ENT=0

B.ENP=1;ENT=1

C.ENP=0;ENT=1

D.ENP=0;ENT=0

第8题

设计一个可控同步计数器,M1、M2为控制信号,要求:

(1)M1M2=00时,维持原状态;

(2)M1M2=01时,实现模2计数;

(3)M1M2=10时,实现模4计数;

(4)M1M2=11时,实现模8计数。

第10题

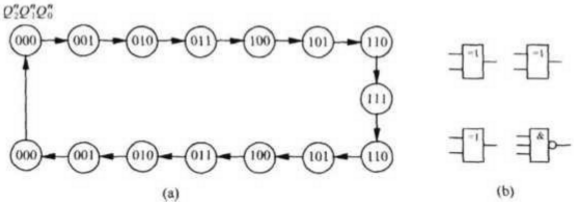

用集成电路芯片74LS161设计一个计数器,自动完成3位二进制加/减循环计数,状态转换图如图T9.4-1(a)所示,要求只能用三个2输入异或门和一个3输入与非门实现,如图T9.4-1(b)所示。

提示:将74LS161的输出作为输入变量,3位二进制加/减循环计数器的状态作为输出变量,列出状态转换真值表,其中状态1000不用,并用端作为加/减转换控制。