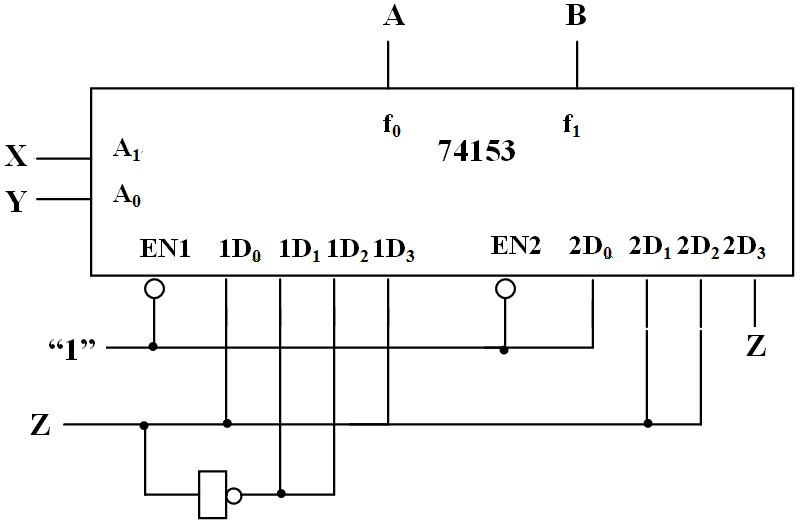

题目内容

(请给出正确答案)

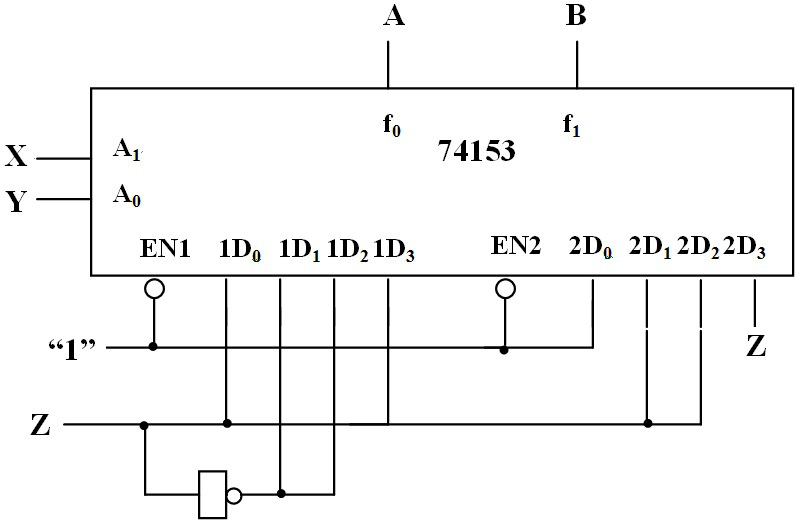

题目内容

(请给出正确答案)

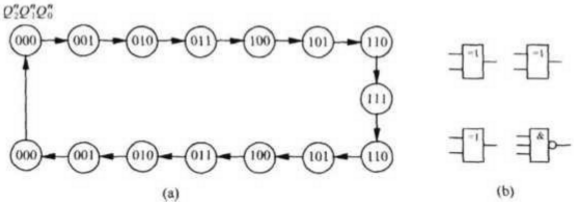

用集成电路芯片74LS161设计一个计数器,自动完成3位二进制加/减循环计数,状态转换图如图T9.4-1(a)所示,要求

用集成电路芯片74LS161设计一个计数器,自动完成3位二进制加/减循环计数,状态转换图如图T9.4-1(a)所示,要求只能用三个2输入异或门和一个3输入与非门实现,如图T9.4-1(b)所示。

提示:将74LS161的输出作为输入变量,3位二进制加/减循环计数器的状态作为输出变量,列出状态转换真值表,其中状态1000不用,并用端作为加/减转换控制。

答案

答案

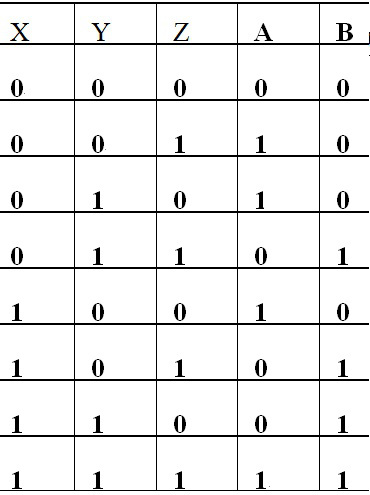

74LS161是一个4位二进制加计数器,要用其实现3位二进制加/减计数器,应可设74LS161的输出为Q3Q2Q1Q0,3位二进制加/减计数器的输出为Y2Y1Y0,则电路的状态转换真值表如表T9.4所示。表中当Q3Q2Q1Q0=0111时,直接跳转换1001,从而得电路的输出方程为

| 表 T9.4 | ||||||

| 输入 | 输出 | |||||

| Q3 | Q2 | Q1 | Q0 | Y2 | Y1 | Y0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | |||

| 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

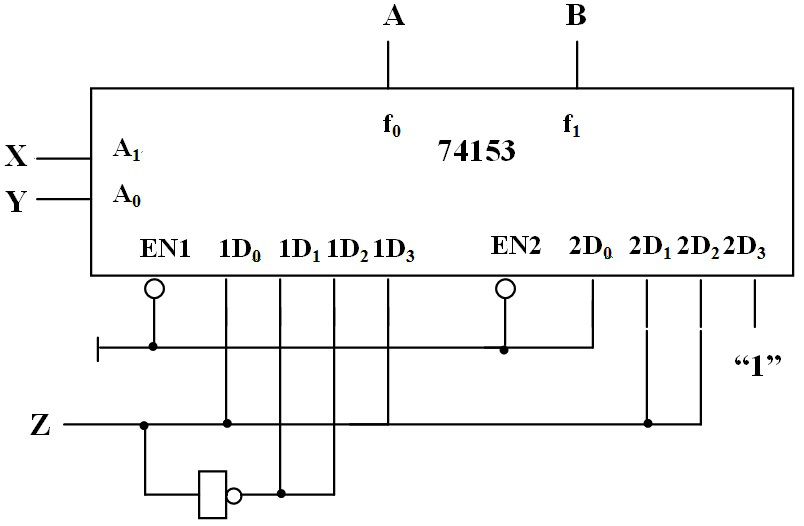

电路图如图T9.4-2所示。