题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

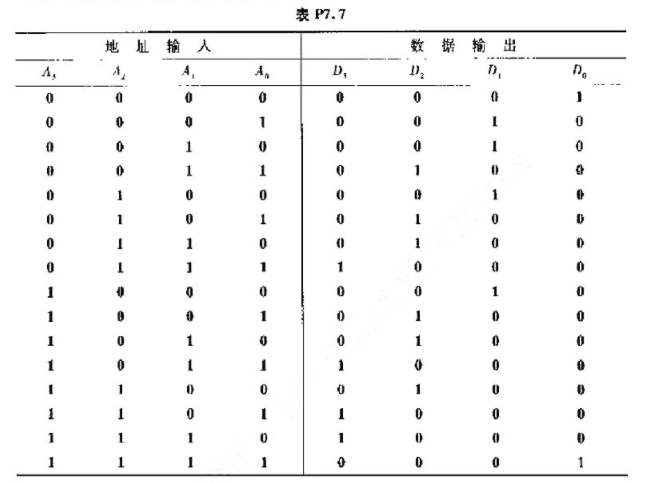

地址输入端为8、数据输出端为4的ROM芯片,其存储容量应表示为()。

A.16×4bit

B.32×8bit

C.256×4bit

D.512×8bit

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.16×4bit

B.32×8bit

C.256×4bit

D.512×8bit

答案

答案

更多“地址输入端为8、数据输出端为4的ROM芯片,其存储容量应表示为()。”相关的问题

更多“地址输入端为8、数据输出端为4的ROM芯片,其存储容量应表示为()。”相关的问题

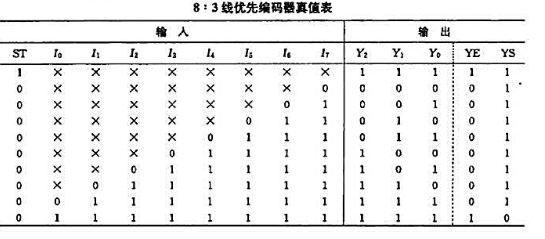

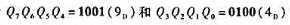

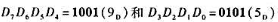

第3题

8:3线优先编码器真值表如下表所示,其中l0~I7为数据输入端(优先级I7为最高),ST为使能输入端,Y0~Y2为数据输出端,YE、YS为输出扩展端.用VHDL语言设计之.

第4题

第6题

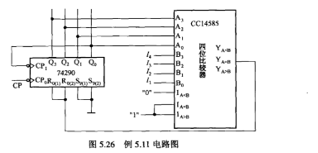

图5.26所示为一可变进制计数器,其模数受I4I3I2I1控制.其中,74290已通过将CP1与Q0短接而连成8421BCD码十进制加法计数器的形式,CP0为外部计数输入端, 为异步置0端,

为异步置0端, 为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端,

为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端, 为扩展输入端,

为扩展输入端, 为比较输出端.

为比较输出端.

(1)分析I4I3I2I1=0110时,该电路为多少进制计数器,并画出其状态转换图.

(2)简述该可变进制计数器的工作原理.

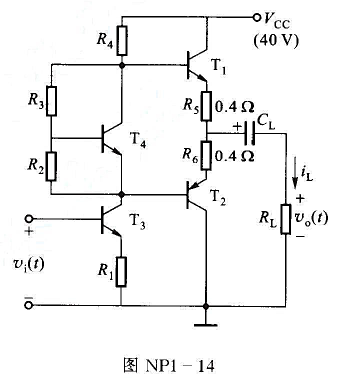

第7题

采用2DPSK方式传输二进制信息.设发射信号振幅A为5V,接收端带通滤波器输出噪声功率

要求系统误码率Pe=10- 4、若采用差分相干解调方法接收该2DPSK信号.试求从调制器输出到解调器输入端信号的容许衰减量。

要求系统误码率Pe=10- 4、若采用差分相干解调方法接收该2DPSK信号.试求从调制器输出到解调器输入端信号的容许衰减量。

第9题

第10题

试用1片八D锁存器74HC373设计一个能锁存两组BCD码信号的锁存电路。假定三态输出使能端 ,锁存器原输出为

,锁存器原输出为 ,输入为

,输入为 ,画出锁存器锁存新数据前、后使能端LE应输入的波形和相应Q0的波形。

,画出锁存器锁存新数据前、后使能端LE应输入的波形和相应Q0的波形。

第11题