题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

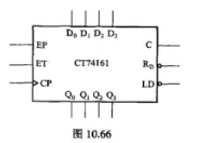

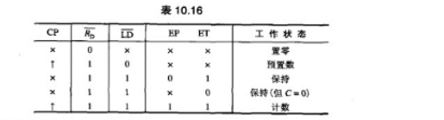

设计5位可变模数计数器。设计要求:令输入信号M1和M0控制计数模,即令(M1,M0)=(0,0)时为模19加法计数器,(M1,M0)=(0,1)时为模 4 计数器,(M1,M0) =(1,0) 为模10加法计数器,(M1,M0)=(1,1)时为模6计数器。

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“设计5位可变模数计数器。设计要求:令输入信号M1和M0控制计数模,即令(M1,M0)=(0,0)时为模19加法计数器,(M1,M0)=(0,1)时为模 4 计数器,(M1,M0) =(1,0) 为模1…”相关的问题

更多“设计5位可变模数计数器。设计要求:令输入信号M1和M0控制计数模,即令(M1,M0)=(0,0)时为模19加法计数器,(M1,M0)=(0,1)时为模 4 计数器,(M1,M0) =(1,0) 为模1…”相关的问题

第1题

第2题

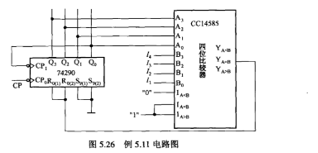

图5.26所示为一可变进制计数器,其模数受I4I3I2I1控制.其中,74290已通过将CP1与Q0短接而连成8421BCD码十进制加法计数器的形式,CP0为外部计数输入端, 为异步置0端,

为异步置0端, 为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端,

为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端, 为扩展输入端,

为扩展输入端, 为比较输出端.

为比较输出端.

(1)分析I4I3I2I1=0110时,该电路为多少进制计数器,并画出其状态转换图.

(2)简述该可变进制计数器的工作原理.

第3题

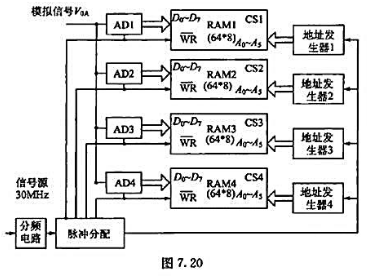

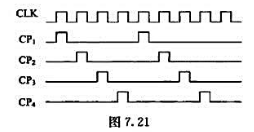

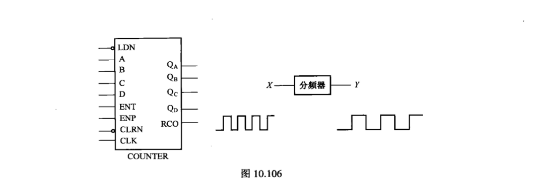

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

第4题

第9题

第10题